・そんなところで、SignalTapを試してみる。XilinxでいうILAと同じようにFPGA内部にろじっくアナライザ相当の回路を組み込んで内部メモリに波形を取り込み、JTAG経由でPCに転送して表示しようというもの。

・Xilinxはあれやこれやと面倒だったのだけどAlteraはどうだろう。

・と、やってみるとなんとシンプルなこと。

1)とりあえずFile=>NewでSignalTapのファイル(*.stp)を作成してSave Asでいったん空ファイル状態でセーブ。

2)右側のSignal Configurationでクロック信号になるものやら取り込みサイズやらを指定

3)左側のところでダブルクリックして観測したい信号やらトリガ条件を追加

4)ビルド

5)右上で.SOFファイルを指定

6)書き込み

7)左上のRun Analysisボタンをクリック

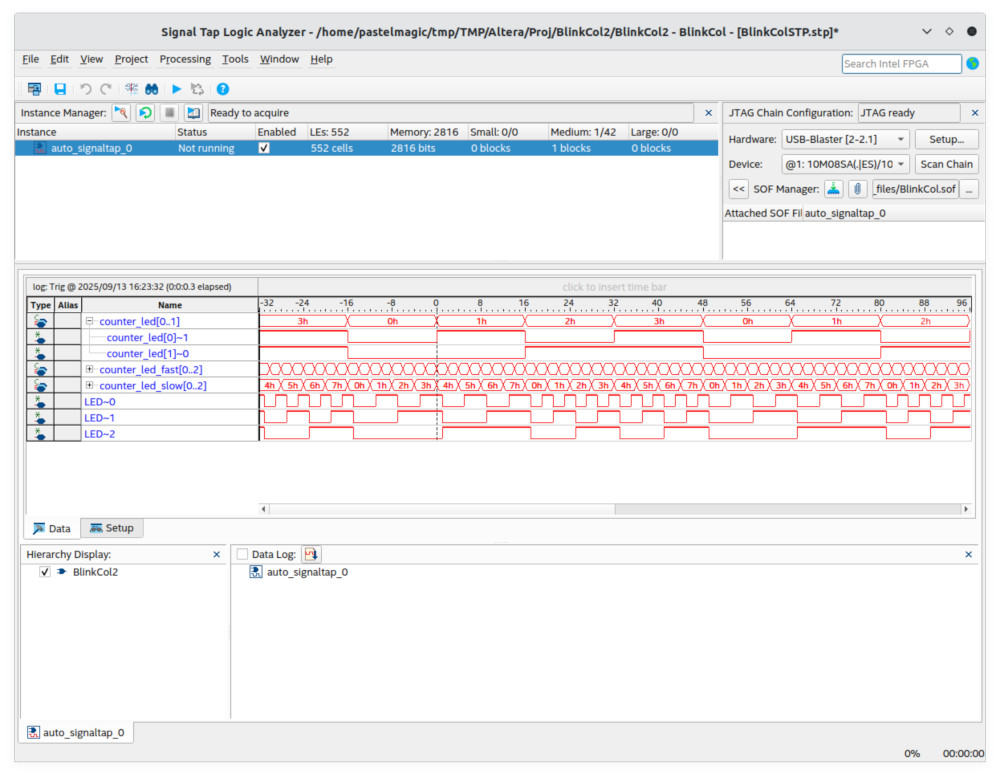

という感じで動かすとこんな感じ。

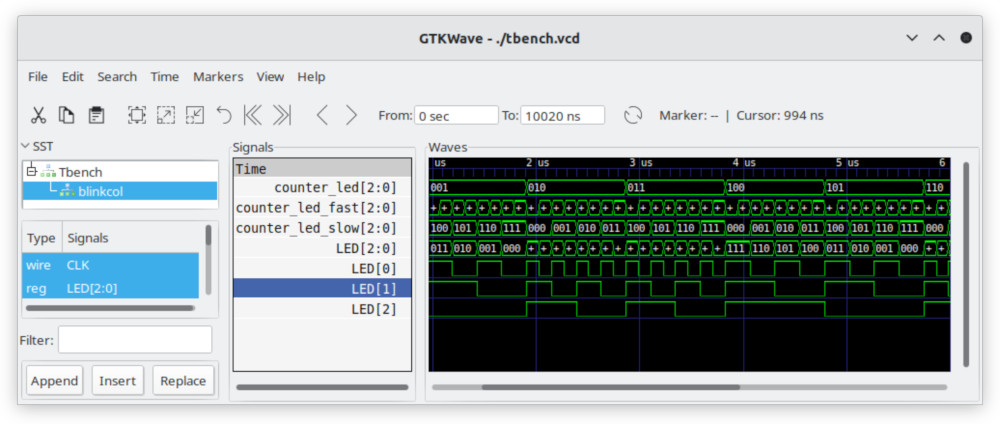

Icarus Verilogでシミュレーションしたときのがこんな感じでまずまず同じ感じ。

・やはりQuartusの方がシンプルだな。最初に触れたFPGAがXilinxのXC3000シリーズだったな。XACTなんてあったっけとか、いろいろ思うけど、やはりこの差を見ているとこれからAltera推しでいこうかな。ブート用の外付けROMも要らないし。という気になる。