2025.09.30 17:30

Verilatorをお試し(まずはlint-only)

・いろいろやっていくと、DSimの甘さが気になってきた。存在しない信号に接続してもだんまりというのが一番大きい。

・更に、これは自分の問題かもしれないけど、ハンドシェークを書いていて相手からのACKを受けたポートを内部信号にalways_combで非同期で取り込んでいるはずなのに1クロックディレイがある。この1クロック分というのがステートマシンの動作クロックで、確かにこの中でACKを見ているけど、そのせいでラッチが生成されるのだろうかな。

・ということで、他のシミュレーション環境は?と思っていて

Verilatorに手を出してみることにした。

・VerilatorはVerilogからC++やSystemCに変換してシミュレーションするという代物。今までIcarusで別段不自由無いくらいだったけど良い機会だから試してみよう。

・インストールはSynapticパッケージマネージャを開いたらVersion4.038があったからとりあえずこれで良いかな。

・サラッと終わったので、今までDSimしていたもので

verrrilator -lint-only testsv.sv

てな具合でlintしてみたら、いきなり

Unsupported: Interfaced port on top level module

と叱られた。トップモジュールでinterfaceを使うのはご法度なのか。

・ということでGeminiに問い合わせ(最近依存しているな)てみると、IEEE 1800-2017などを厳密に解釈するとinterfaceは「どこかとつながっている」ことを前提とした仕様だというお話。なるほどね。なんとなくすっきりした。

・ということで、一枚皮をかぶせることに。今までのトップモジュールを下位に追いやって、テストベンチで接続していたinterfaceをトップモジュールで接続。どうせ下位モジュールの信号も全部見られるのだからこれで問題ない。

・ということで書き換えてみたらverilatorのエラー消滅。

2025.09.29 17:08

DSimのオプション

・そんなこんなで、VSCode上でDSimを使ってみている。

・シミュレーションのオプションで、前はーLオプションでテストベンチのトップモジュール名を指定するということだったのだけど、

-top work.tbench +acc+b -waves testsv.vcd

てな具合にーLオプションを外していても出てきたVCDファイルは同じだった。

2025.09.28 09:07

汎用人型・・・

・汎用人型ロボットの開発を支援するという。出所は経産省などでもなく「内閣府」。いわゆる「ムーンショット計画」の一つらしい。

・遅い・・・とは思うけど遅すぎるということはない。

・人口減少に伴う人で不足を移民で補うのではなく、技術革新で乗り切るというのはとりあえず正しい方向ではある。

・ついでにいえば、米づくりなどで「小規模が多いから集約・機械化はできない」と言っているけど、そちらも機械の側が対応するようにしていく手もある。

・「無理だ、不可能だ」「できるわけがない」という言葉は昔からいろいろな分野で聞いてきたけど、本当にできなかったものは(理論的に絶対無理な永久機関の・ようなもの以外)さほど無い。

・ところで汎用人型・・・と聞くと「決戦兵器」が後に続くのではないかと思ってしまうエヴァ世代だったりするけど、そちら方面が頭の中に無いと言えば嘘になるだろうな。もちろん「巨大」ではない。実際犬型のロボットはウクライナで活動しているようだし。

・などと書いていて様々な巨大ロボットたちが土木工事をしている姿をふと想像してしまったりするのだった。散らかしたら片付ける、壊したら直す・・・だな。

2025.09.27 20:38

2000円代のFPGAボードか

・タイミング制約のやりかたがわかってきたのでやってみたらホールド時間で文句を言われてしまった。これはどうやって制約決めるのかな。

・なんとなくFPGAボードを検索していたら、6000LEクラスのCycloneを使ったボードが

Amazonで2300円程度であった。1LE=12ゲートとすると7万2千ゲートというところか。

・ちょっと食指が動きそうになるな。

2025.09.26 14:48

MAX10でPLL

・MAX10でPLLを使ってみることに。

・プロジェクトをコピーしてみたらソースコードは元のディレクトリを参照していた。いったん削除して指定しなくてはならない

・更にAnalysis & Synthesisしてピン配置を見たら初期化されてしまっていた。毎回設定するのも面倒だなと思ったら、CSV形式でエクスポート/インポートできるそうで。試しにエクスポートしたら、ご立派なコメント付きのCSVファイルができていた。既存のものからこれをいただけば良いのだな。

・これで合成して動かしてみたらちゃんと動いた。

・そして・・・PLLはAlteraのIPをウィザードのようなものを使って取り込めば良いのか。

・とりあえず現状の48MHzから100MHzを生成してみるか。

・チェックボックスをちょっといじらないといけないところもあるけど、スッキリしていて難しくはない。

・モジュール名とポートはソースを見ればわかるので、これをインスタンス化してポート接続すれば良い。

・って、こんなので良いのか?とコンパイルするとすんなりエラーなし。ならばと合成して動かしてみたらちゃんとほぼ倍速動作。

:調子に乗って200MHzにしたら超高速点滅。

・あとはタイミングの制約とチェックができれば、現状の合成レポートの赤字(クロック周波数の制約を入れていないので)も消せるかな。

2025.09.26 21:14

不良品ビジネス

・というところで、ロシアに対して西側の半導体を入手する抜け穴があって結構手に入っているという話がある。

・一方で、過日キーウに対して行われた攻撃でミサイルがちゃんと爆発しなかったということがある。

・ふと思うのは、抜け穴の一つとしては中国があることはほぼ確実だろうけど、あそこは言うまでもなく偽物天国で、以前の半導体不足のときも生産ラインではねられたものがそのまま流通してしまっていたり、中身が入ってないものや全く違うダイが入ったものなど、もはやなんでもありだったこと。

・ふと思ったのは、喉から手が出るほど欲しい、金はいくらでも積むというのを相手にして、こういう不良品、偽造品を売りつけるというのは平然と行われているのではないかなということ。

・わざわざ正規品を入手するより、こうしたまがい物のほうが圧倒的に「仕入れ値」は安いわけだ。もちろん簡単な検査でわかるような不良だとバレるけど、温度特性が悪いなどスペックをちゃんと満たさないものや、検査項目に引っかからない(商業用のロケットなどと違うから検査項目も多くはないだろう)あたりなら実際に動かすまでわかりはしない。

・不良品を大量に売りつけておいて、発覚する頃にはドロン(死語?)というのもあながち無いとは言えないのではないかなとふと思うのだけど、どうなのだろう。

・ドローン部品納入業者がドロン・・・というジジイギャグはやめておこう。

2025.09.25 07:07

Inkscapeのハンドル調整

・Inkscapeを使っていて矩形などを配置したときにコーナー部分に四角や丸のハンドルが表示されるのだけど、これが大きすぎてみっともないしなんとなく使いにくい。

・大きさを変えられないのかと検索したけど見つけ方がよくわからないのでまぁあるとすれば環境設定だろうと開いてみたら日本語化したときと同じところの下に「ハンドルの大きさ」設定があった。なるほどね。サイズ4くらいでいいかな。

・少しいじってみているけど結構ご機嫌で使えそうだな。

2025.09.24 06:43

Inkscape1.5をインストール

・ドローツールを検索してInkScapeがおすすめっぽいのでパッケージマネージャで見たらSynapticパッケージマネージャで見ると1.1.2-3Ubuntuがあったのでインストールしてみる。機能はたくさんあるのだろうけど、Word図などのレベルである程度間に合っていたレベルでいじってみていると難しくない。アイコンやメニューを眺めてマウスでゴニョゴニョするとまぁそうなるよねという動き。

・これはいけるかなと思いながら検索していると1.4などが出ている模様。

・ひょっとして「Ubuntu Software」側にないかなと思って起動してみたら1.4がでてきたので、1.1をアンインストールっっして1.4をインストール。さて、日本語化はできないのかな?とこれまた検索するとEdit -> Preference -> Interfaceで日本語を選べば良いということなのだけど、やって再起動してみても変化しない。

・別に自分が使う範囲では英語でも構わないのだけど、なんでかなと思いながらUbuntu Softwareで「ソース」のストアを開いていたら1.5が見つかった。ひょっとしてFixされているかな?と1.4をアンインストールして1.5をインストール。

・これで同じようにやったらすんなり日本語化された。これでいいかな。

2025.09.23 06:58

原稿の図版カキカキ

・世間では休日だったのだな。すっかり忘れていた。

・原稿依頼があったので、とりあえず図版から。Wordで図を描いてしまっているけど、ドロー系の良いものはないかな。

・そんなことをしながらウクライナ情勢を見ていると、ウクライナがかなり派手にロシアの石油生成施設やらパイプライン、港湾を無人機で攻撃している模様。

・生成能力の50%近くを失ったということだけど、これはこれからも増えていくのだろう。ガソリンや軽油などもだんだん供給がまずくなっているようでもある。モスクワは物資流通のハブになっていることもあって最後まで枯渇しないように粘るのだろうけど、その他の地域では車も農作用の機械類も動かせない、真冬の暖房はどうするのだろうといろいろ想像してしまう。

2025.09.22 06:48

多摩御陵参拝

・少し気温が下がってきたこともあって、ちょっと出かけついでに今まで通り過ぎるだけだった多摩御陵に初めて立ち寄ってみた。これは「参拝」というのか、なんだかよくわからないけど、適当な言葉が思い浮かばなかったのでとりあえず「参拝」。

・どこに停めたら良いのかよくわからないような広々とした駐車場に車を置いて足を踏み入れるといきなり別世界。

・砂利の音をたてながら少し歩くと分岐が見えてきたので、一番奥から順に。

・一回りするとなんとなく心洗われたような感じもする。

・といいながら、数分後には「もち吉」で賞味期限間近なお値下げ品煎餅を買ったりしているのであった。

2025.09.21 06:38

CF Expressカードがやってきた

・オシロスコープのCFカードのリーダーがちょっと怪しん雰囲気。

・そんなところでCFカードを探しているうちにひょんなことからCF Expressのカードをもらってしまった。結構な大容量である。

・もう、メモリカードの類なんてSD/MicroSDしか付き合いがなかったのでまったく追っていなかったのだけど、CFカードとは全く関係ないし、TypeA/B/Cとバラバラ。

・さて、こいつを読めるものは?と思って検索したら全タイプ対応というのはほとんど無くて、A/B/Cそれぞれに対応製品がある。圧倒的に多いのがType-Bで、マルチで対応するものもType-BとSDカードというのが多いようだ。

・Googleで検索すると最初にAIによる回答がついてくるけど、そこではType-AはSONY、Type-Bはその他メーカーのデジカメが対応っていうことで、β/VHSなのかレーザー/VHDなのかというあの時代を思い出させてくれたりする感じになっているようだ。

・いただいがのがType-Aなので、Type-Aのリーダーライタを調達。ついでにCFカードリーダーの方も。しかし、このCFカードがお亡くなりになったらどうするかな。CFカードからの変換アダプタをつけることになるのかな。

2025.09.20 22:29

SystemVerilogのinteraceもうちょい

・そんなところで、SystemVerilogで書き直したLED点滅を書き込んで動作確認したり、LogicTapで内部波形を観測というところまでうまくいった。

・SystemVerilogのinterfaceの中にもalways_ff()などを使ってロジックを書くことはできるということを知る。しかし、これも使いみちはというと限定的なのかな?という感じ。

・interfaceがお役立ちなのはモジュール間のインターフェース、簡単に言えば通信回線の定義で、interfaceで定義したものを使えば簡単に相互接続できる。

・送信側と受信側で信号の方向が違うのはinterface内でmodportを使ってそれぞれの信号の向きを変えたものを定義して

.

って感じで、どれ(どっち)を使うのか決めれば良い。

・たとえば、バスクロックはマスタ側が出力、スレーブ側が入力なら、

interface mybus;

logic bclk;

・・・・・

modport master(output bclk, ・・・);

modport slave(input bclk, ・・・);

endinterface

なんて具合にして

module blk0(mybus.master busout);

・・・・

endmodule

module blk1(mybusss.slave busin);

・・・・

endmodule

まぁ、こんな感じにしておいて、後でこいつらのインスタンスをこしらえてやれば良い。

・でも、ここで、interfaceの中で

always_ff @(posedge clk) begin

bclk <= =bclk;

end

(実際にはもっと分周するだろうけど)

なんて具合にbclkを駆動してしまうと、slaveの方で入力としているのと辻褄が合わなくなる。

・ということで、こいつが使えるのはバスで結線する時に両方とも入力となる時なのかなぁとも思うけど、それで何らかの処理をした信号を出力しようとすると、結線したときに衝突してしまうわけだし。まぁ、そのうち使いみちも見つかるかな。

2025.09.19 12:37

DSimをお試ししてみる

・SystemVerilog対応なシミュレータということで、Quartus上ではQuestaがご推奨のようなのだけど、なぜか起動してくれない。

・もうちょっとなにか無いのかなと思って探していたらDSimというのがあった。

・

VSCodeのプラグインとして実装されているもの。

・丸文さんが作成した

GOWIN用のチュートリアルでも使われているので、まぁさほど怪しいことはないのだろう。

・検索してみると単独で起動して使うこともできそうだけど、とりあえずプラグインとして使ってみることにしよう。

・で、VSCodeのプラグインなので、いつものとおりやれば良いのだろう。FPGAの開発環境のところにはインストールしていなかったけど、Ubuntu Softwareにあったので、簡単インストール。ExtensionsでDSimを探してインストール。とりあえずエディタのキーバインドもVimにしたいので、Vimもついでに。(個人的にはEmacs風というのか、xyzzyが気に入っていたのだけど、Linux版のxyzzyはリリースされないのだな)

・このあと、ライセンス取得のために

ご本家でユーザ登録をして、VSCode上でポチッとクリックすればライセンス認証完了。このあたりまでは丸文さんのドキュメントでOK。

・さて、とりあえずチュートリアルを・・と思ったらこれがすでに半分出来上がった環境で動かすだけなので1から作るのにはあまり参考にならない。まぁそれでも一応シミュレーションで波形までVSCodeの画面上に出るところは確認できた。

・このあとが結構いろいろあったけど、なんとかIcarusでシミュレーションしたり、Quartusで合成して動作確認していたロジックをDSimでシミュレーションするのはできた。

・ソースコードファイルを登録するのにGUIでクリックでポチポチとはできなくて、../xxx.svなんて具合に書いてやらないといけないのがちょっと面倒う臭かった。

・SIMULATION CONFIGURATIONで右クリックで「Configure Simulation」を選択して、Optionsを

-top work.Tbench -L BlinkCol +acc+b -waves waves.vcd

なんて具合にして(Tbenchがテストベンチのモジュール名、BlinkColがテストベンチがターゲットにしているトップモジュールなのだそうで。+acc+bが波形データを取得するという謎オプション。-wavesで波形ファイル名を指定すると拡張子を見て勝手にフォーマットを決めてくれる。この例なら.vcdで出してくれるので、gtkwaveで見ることができる。

・ちなみに、テストベンチの前についてる”work.”というのはお約束のおまじないみたいだな・・・と思ったら、LibraryConfigurationでソースファイルを追加するとき、LibraryNameのデフォルトがworkだったから、たぶんこれを引きずっているんだな。

・ちょいと引っかかったのがinterfaceの記述で、モジュールポートにinterfaceを使ったような場合に、

interface spi_if.maaster MasterPort;

なんてやるとエラーで、

spi_if.maaster MasterPort;

という具合にしないといけないところ。

・このあたり、もう少し使い込んだから一回まとめておくか。

2025.09.18 08:59

IcarusはInterface未対応か

・SystemVerilogのInterfaceが便利そうだなと思って使ってみようとしたら、構文エラーになってしまう。あれこれ検索するとどうやらIcarus Verilogは対応していない模様。

・とりあえず仕方ないのか。Quartusと一緒にインストールした(はず)のQuestaのAltera版(昔はModelSimだったようだけど)を使ってみるかな。

2025.09.17 22:13

パスワードでゴタゴタ

・さて、ぼちぼち振り込みをやっておくかとネットバンキングしようとしたら「パスワードを更新してくれ」というメッセージとともに更新画面に飛ばされた。

・仕方ない・・・と思ってやろうとしたら取引実行のためのパスワードが間違っているという表示でできない。いや、だって先月の振り込みはここからやっただろう。

・この環境、Windows11にアップデートしたせいなのか、いや、そんなのは関係ないだろうと何度かやってもだめ。

・メッセージは出ないけど、おそらくパスワードロックがかかってしまっただろう。

・さて、それならということで、もう一つの管理者権限側からログイン。こちらはおおよそ1年近く放置していたので、ひょっとしたら電子証明書の期限切れでやばいかも・・・と思ったらギリギリセーフ。

・冷や汗をかきながらログインするとこちらもパスワード更新メッセージ。さて、こちらはどうだったかと思い出しながらやったらやっぱり取引パスワードがだめ。

・ここで一回冷静に・・・ひょっとして前回の更新の時にこういうふうにしてしまっていたかと改めてやったら大当たり。

・落ち着いてとりあえず振り込みを終わらせてからいつも使っている側のIDを見るとなるほどパスワードロックがかかっている。

・そちらに仮パスワードを設定してやって、そちらのPCからログインして改めて仮パスワードを入力して、新しいパスワードを設定。今度はうまくいった。

・冷や汗かいたなぁ。これから気をつけよう。

・やっぱりパスワードは嫌いだ。生体認証にならないものなのかなぁ。

2025.09.16 10:19

SystemVerilogとstructとinterfaceと

・SystemVerilogになって構造体が使えるようになったという。

・それならたとえば、SPIバスのようなものを

typdef struct [

logic sck;

logic cs_n;

logic mosi;

logic miso;

} spi_bus;

のようにしてモジュールポートとして定義できれば美しい・・・と思った直後に入出力方向はどう決めれば良いのだ?ということになった。

・入出力はmoduleのポート宣言でしていするよりないわけで

module xxxx (

output spi_bus SPI_PORT

);

なんてことをすると、SPI_PORTは全部出力になってしまう。

inoutにするというのも美しくない。

System Verilogで構造体メンバに入出力属性をつけられないから仕方ないのか。

・ということで検索したらinterfaceがあるよということを知る。

interface spi_if (input logic clk);

logic sck;

logic cs_n;

logic mosi;

logic miso;

modport master (

output sck,

output cs_n,

output mosi,

input miso

);

endinterface

なんて調子でいけるらしい。

2025.09.15 20:43

ボツボツSPI

・Linux上でPicoScopeも動くようになったし、IcarusVerilogも、QuartusもLinux上で事足りているしで開発環境はほぼほぼLinux上で全部大丈夫そうだな。

・さて、ぼつぼつとSPIスレーブ機能部分でも書くか。デバッグは・・・RaspberryPiあたりをホストにしてやればいいか。

・と手をつけ始めたところで、ステートマシンのステート番号をenumできないのかなというところで、Gemini君に聞いてみるとtypedefできるよという。でもなんとなく変だなと思ってもう少しつついてみたらSystemVerilogなら・・・ということ。

・というあたりで、いままでなんとなくスルーしていたSystemVerilogとご対面となる。

・ごちゃごちゃしたところは生成AI君にお尋ねしてみたけど、あまり欲張らないで使うということなら、wireやregをまとめてlogicにすれば良いとか、structが使えるようになっているとか、Verilog+αてきにいけるようだ。

・ところでQuartusは対応しているのかな?と思ったらLiteエディションでもすんなり対応しているらしい。

・で、IcarusVerilogの方もOKらしい。ちょっと試したらエラーが出たのだけど、これは拡張子svで自動判定とはいかなくて、"-g2005-sv”というオプションをつけてやればOK.ちなみにテストベンチは手を加えずにVerilogのままだけど何も文句は言われなかった。C/C++のような関係なのかな?

2025.09.14 19:31

UbuntuでPicoScope

・というところで、久しぶりにPicoScopeを動かしてみる。

・ソフトは?と見に行ったらPicoScope7がリリースされている。Linux,MacOS,Windowsのフル対応だけど、以前試したときは仮想マシン下のLinuxではうまくいかなかったんだっけとか思いながらつらつらとサイトを眺める。

・インストール方法は説明されているとおりで、特別難しいことはない。要するにリポジトリを登録してsudo apt install picoscopeすればいい。

・実機が無くてもデモモードで立ち上げて適当な入力があるかのようにしてプロトコル解析なども試すことができる。なるほど。

・ということで、実機とつないでみる。やってみたら最初に認識されてから再接続されるのだけど、このとき見つからないよということになってしまう。

・やはりだめなのかと思っていた時にふと「こいつはUSB3.xじゃなかったけ?」と思い出して仮想マシンの設定を見たらUSB2.0になっていた。

・これを変えれば良いのかとやってみたらビンゴだったようで、ちゃんと認識されて動き出した。とりあえずアナログチャンネルを試したら結構簡単にいけそう。

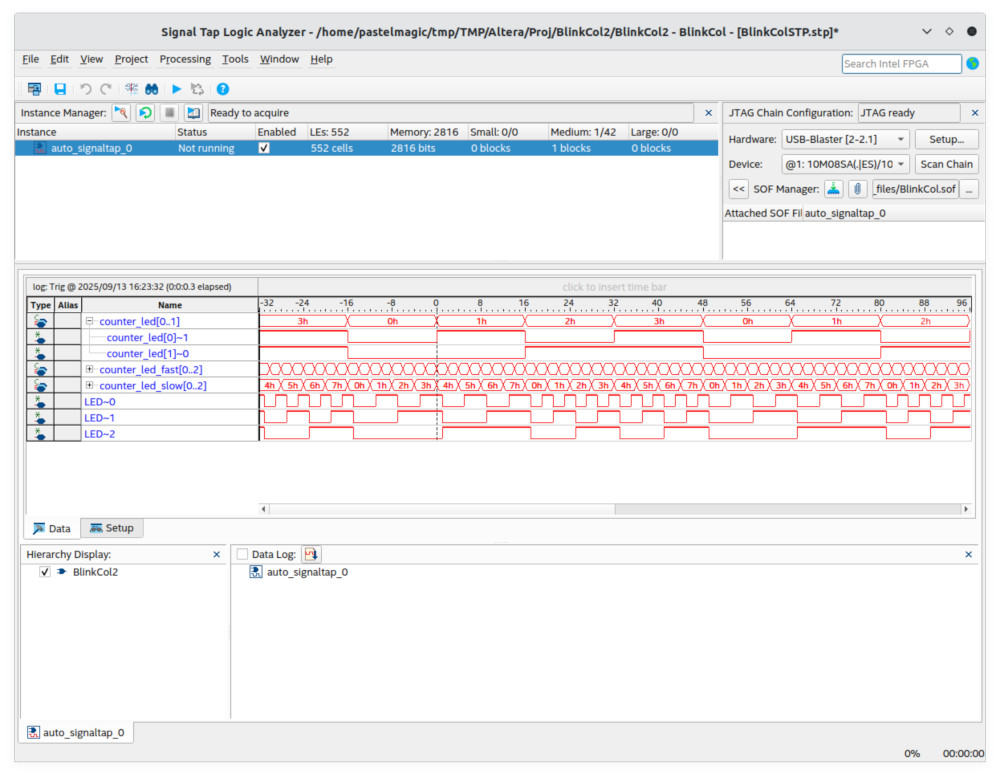

2025.09.13 16:49

簡単じゃないかSignalTap

・そんなところで、SignalTapを試してみる。XilinxでいうILAと同じようにFPGA内部にろじっくアナライザ相当の回路を組み込んで内部メモリに波形を取り込み、JTAG経由でPCに転送して表示しようというもの。

・Xilinxはあれやこれやと面倒だったのだけどAlteraはどうだろう。

・と、やってみるとなんとシンプルなこと。

1)とりあえずFile=>NewでSignalTapのファイル(*.stp)を作成してSave Asでいったん空ファイル状態でセーブ。

2)右側のSignal Configurationでクロック信号になるものやら取り込みサイズやらを指定

3)左側のところでダブルクリックして観測したい信号やらトリガ条件を追加

4)ビルド

5)右上で.SOFファイルを指定

6)書き込み

7)左上のRun Analysisボタンをクリック

という感じで動かすとこんな感じ。

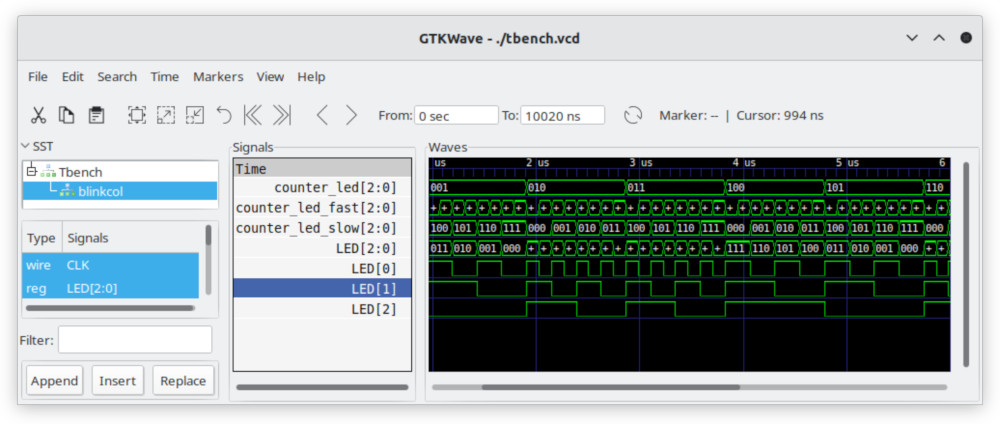

Icarus Verilogでシミュレーションしたときのがこんな感じでまずまず同じ感じ。

・やはりQuartusの方がシンプルだな。最初に触れたFPGAがXilinxのXC3000シリーズだったな。XACTなんてあったっけとか、いろいろ思うけど、やはりこの差を見ているとこれからAltera推しでいこうかな。ブート用の外付けROMも要らないし。という気になる。

2025.09.12 11:24

always @(*)

・verilogでalways @(*)を使えばcaseやらifを使った非同期なセレクタの記述が簡単になるのだけど、果たしてQuartusは対応しているのだろうかとお試ししてみる。

・とりあえずIcarusVerilogのシミュレーションではうまくいっているようなので、QuartusでカラーLEDの点滅パターンを変えて書き込んでみたらうまく動いた。

・さて次はSignalTapでも試してみるか。AMD/Xilinxの方はこのあたりも結構面倒くさかったけど、Intel/Alteraはどうかな。

2025.09.11 15:26

MAX10評価ボード

・MAX10を使うことがほぼほぼ確定。いままで付録基板みたいな小規模なものでいろいろやっていたけど、ぼちぼち少し規模の大きい評価ボードを入手しておく必要がありそうだな。

・なんて思いながら探していたDK-DEV-10M50Cとかいうものが見つかった。DigiKeyで在庫があるらしい。送料含めたらマルツさん経由の方が割安かな。しかし、ご本家Intelさんの写真とマルツさんの写真が違うのは何なのだろう。

・いきなりの豪雨で焦る。都心方面はかなりすごいことになったところもあったようだけど、こちらは普通にすごい雨という程度で、30分もしないうちに僅かなポツポツ雨。

2025.09.10 14:57

ポータブルHDDの収納袋

・少し整理していたらWiMAXのルーターを入れるのに使っていたポーチというのか、ファスナー付きの入れ物が出てきた。

・なんとなく2.5インチのポータブルHDDとサイズが入りそうだなと思って試しに入れてみたらぴったりすぎるくらいのシンデレラフィット。少々キツめだけど外側のポケットにケーブルも押し込めた。

・しかし、まるでHDDっぽくないな。

2025.09.09 06:23

matplotその後

・matplotで一応それっぽいグラフは描けるようになってきた。

・なぜそうなっているのかなと謎なところもあるけど、まぁ良いとしよう。

・まだちょっとわかっていないのが数学の直行座標的にX軸、Y軸・・・x=0とy=0だけを太くしてやる方法。

・グラフの範囲を決めて、その範囲でx=0とy=0のグラフを描いてやれば一応それっぽくできるけど、やり方が美しくない。

2025.09.08 06:17

記憶力は大丈夫そうか

・忘れていたと思ったけど、英単語は頭に残っていた。まだ記憶力はそれなりに大丈夫というのか、昔よりマシそうだなと思っておこう。

・Intelは不調だというけど、ノートPCなどでは相変わらずIntel Coreが多いような感じがするのはなぜだろう。法人向けは安い・・・のかな?

2025.09.07 19:33

matplot

・ちょっとグラフを入れ込もうと思ってあれやれこや。gnuplotでいくかとも思ったけど、ちょっと思い立ってpython+matplotしてみる。

・インストール時についmathplotとしてしまって「そんなもん無いよ」と言われてしまったりと、ちょっと躓いたけど、なんとかインストールできた。

・matplotは多機能すぎてややこしいけど、とにかく目的が達成できれば良しということで、必要最小限の範囲でぼちぼちと調べながらやっていこう。

・とりあえず

import matplotlib.pyplot as plt

とやっておいて、あとは、xとyのデータ列リストを作って

plt.plot(x,y)

とでもすればグラフはできる。

あとは軸の目盛りとか凡例とか細かい調整をやれば良い。

・雛形ができればあとはデータ列の差し替えをするだけだしな。

m

2025.09.06 20:47

記憶力や如何に

・そんなこんなで、少し勉強モードで英文のドキュメントを眺めたり。

・そういえばとなんとなく昔ちょっとやっていたDuo3.0を引っ張り出してみたらそこそこ忘れている。記憶力低下のテストを兼ねて少しやってみて、明日にでも復習してみたらどうなるか様子を見てみるかな。と書いていて、そもそも昔も記憶力なんて全然良くなかったじゃないかと自分にツッコミを入れていたりして。

・というところで学校関係の課題の採点をする。コピペしたなと明らかにわかるものも多々あるのだけど、まぁそれはそれなりに低評価ということで。

2025.09.05 12:42

ノートPCアップデート

・コピーが終わったので、ノートPCのアップデートをしておく。ほったらかしておいたら終了して、再起動していたのだけど、なぜかPC購入時の最初の気道のようなメッセージが次々に・・・・

・アップデートにしては変だなと思った後、起動した画面まで違っている。

・winverしてみたらWindows11になっていた。それなりに昔に買ったものなのでWindows11には対応していないと思っていたけど対応していたらしい。

・ということは、ディスプレイがお亡くなりになったあれも対応か。修理するかなぁ。正規で頼むと7万円超え。修理専門業者に依頼してみるかどうするか。

2025.09.04 16:32

波動散乱の逆問題

・「波動散乱の逆問題」が随分前に神戸大学 教授の木村建次郎先生によって解決され、実用化されてきていることを知る。

・物体に当たって散乱された波動からどこにどんな形状のものがあるのかを逆算・推定できるというのだから、簡単に言えば「全方位3Dスキャナ」みたいな感じか。ほんの僅かな散乱でも影響がわかるわけで、あらゆる産業で革命だな。・視覚・聴覚にも、どうかしたら触覚さえも革命が起きてくるのかもしれないな。いろいろ良からぬ使い方も頭に浮かぶけどね。

・そんなところでHDDのコピーを始めて24時間経過した時点で30%しか進んでいない。ちゃんと進んではいるけれど、こんな調子で大丈夫かな。

2025.09.03 16:11

LibreOffice Writerでテキストリンク

・LibreOfficeのWriterで複数のテキストボックスの間をリンクさせてみようとしたのだけどなかなかやり方がわからない。

・Wordだったら、リンク元のテキストボックスを選択して上のチェーンのようなアイコンクリックして、リンク先を指定するだけなんだけど。

・Google先生に尋ねてもなかなか見つからないし、無理だろうとなと思いながらChatGPTやらGeminiやらに尋ねてもやっぱり頓珍漢。

・でも、この程度のことは機能的にはあるはず。

・それならばということで、いったんWordでテキストボックスのリンクのあるものを作成して.odt形式やdocx形式でセーブ。これをWriterで読み込んだらどうなるだろうとやってみる。

・なんと、なんとなくうまくできている。リンクの線も表示される。ということは機能としては持っているということだ。

・あとはひたすら探すだけ。「挿入=>フレーム=>対話的に枠を挿入」して、右クリックのプロパティで枠に名前をつけておいて、連結元や連結先を指定すれば良いのか。

・そんなところで、1万円ちょいの4Tバイトの外付けHDDが到着。中身は3.5インチなのだろうけど、やっぱり大きいな。まぁバックアップ用だから良いけど。

・さっそく先日作成した仮想ディスクをコピー。さらに今まで使っていた2TのHDDのまるごとコピーをすることに。時間が延々とかかるのはわかりきっているので、今まで休眠状態だったら昔使っていた富士通さんの大きめノートPCを引っ張り出してきてコピーマシンとして活用。さて、どのくらいで終わるだろう。

ど、これがなかなか進まない。容量が大きいから仕方ないか。

2025.09.02 13:10

Verilogテストベンチでちょいミス

・テストベンチとの間でハンドシェークさせているはずなのに動きがおかしい。なぜだろうと追いかけていったらリセットするのを忘れていた。リセットしなくても、ステートはdefaultのおかげでそれなりに安定していたけど、他のところはだめだったんだな。

・ついでにハンドシェークもハンドシェーク信号を先取りしていた部分が勝手に先に進んでしまっていたのが原因だった。こちらもちゃんと整合させた。

・気づいてしまえば簡単。ただ、このおかげで予定外の入力があるとおかしな挙動になることがわかったのは利点か。

・さて、Windows11化した環境下でネットバンキングがうまく行くのかとやってみる。ちょうど電子証明書も更新が必要ということなので、やってみることに。朝やってみたら「この時間はだめ」と言われてしまったけど、改めてやり直してみたら無事に更新できた。

・いったんログアウトして再ログインしても大丈夫だったので、これでOKだろう、たぶん。

2025.09.01 09:30

バックっルームコンプリート

・RobloxのThe backroomsでコンティニューがわからなかったのが、実は最初の画面のたくさんのドアというのか入口っぽいのがそれぞれの面につながっている(まだ到達していない面には入れない)ということがわかってやっと先に進めるようになった。

・で、なんとか全部クリア。なんだか面白かったのかなんだったのか。まぁ、「こういうものだ」というのはよくわかった。

・そんなところで、Verilog。テストベンチで@posedgeが使えるのでやってみたらうまくいかない。なぜかなと思ったら直前の状態が”X"。そうか、初期化を忘れていたか。

・先日買ったリューターで100均のリューターのビットというのかパーツが使えるのかな?と思ったら口のところ(コレット)の直径が合わない。当然のようにアダプタが売っていたので入手してみることに。楽天だと楽天ペイにチャージしたのが使えるのか。試してみようとやってみたら本当に使えた。なるほど。