2025.09.17 22:13

パスワードでゴタゴタ

・さて、ぼちぼち振り込みをやっておくかとネットバンキングしようとしたら「パスワードを更新してくれ」というメッセージとともに更新画面に飛ばされた。

・仕方ない・・・と思ってやろうとしたら取引実行のためのパスワードが間違っているという表示でできない。いや、だって先月の振り込みはここからやっただろう。

・この環境、Windows11にアップデートしたせいなのか、いや、そんなのは関係ないだろうと何度かやってもだめ。

・メッセージは出ないけど、おそらくパスワードロックがかかってしまっただろう。

・さて、それならということで、もう一つの管理者権限側からログイン。こちらはおおよそ1年近く放置していたので、ひょっとしたら電子証明書の期限切れでやばいかも・・・と思ったらギリギリセーフ。

・冷や汗をかきながらログインするとこちらもパスワード更新メッセージ。さて、こちらはどうだったかと思い出しながらやったらやっぱり取引パスワードがだめ。

・ここで一回冷静に・・・ひょっとして前回の更新の時にこういうふうにしてしまっていたかと改めてやったら大当たり。

・落ち着いてとりあえず振り込みを終わらせてからいつも使っている側のIDを見るとなるほどパスワードロックがかかっている。

・そちらに仮パスワードを設定してやって、そちらのPCからログインして改めて仮パスワードを入力して、新しいパスワードを設定。今度はうまくいった。

・冷や汗かいたなぁ。これから気をつけよう。

・やっぱりパスワードは嫌いだ。生体認証にならないものなのかなぁ。

2025.09.16 10:19

SystemVerilogとstructとinterfaceと

・SystemVerilogになって構造体が使えるようになったという。

・それならたとえば、SPIバスのようなものを

typdef struct [

logic sck;

logic cs_n;

logic mosi;

logic miso;

} spi_bus;

のようにしてモジュールポートとして定義できれば美しい・・・と思った直後に入出力方向はどう決めれば良いのだ?ということになった。

・入出力はmoduleのポート宣言でしていするよりないわけで

module xxxx (

output spi_bus SPI_PORT

);

なんてことをすると、SPI_PORTは全部出力になってしまう。

inoutにするというのも美しくない。

System Verilogで構造体メンバに入出力属性をつけられないから仕方ないのか。

・ということで検索したらinterfaceがあるよということを知る。

interface spi_if (input logic clk);

logic sck;

logic cs_n;

logic mosi;

logic miso;

modport master (

output sck,

output cs_n,

output mosi,

input miso

);

endinterface

なんて調子でいけるらしい。

2025.09.15 20:43

ボツボツSPI

・Linux上でPicoScopeも動くようになったし、IcarusVerilogも、QuartusもLinux上で事足りているしで開発環境はほぼほぼLinux上で全部大丈夫そうだな。

・さて、ぼつぼつとSPIスレーブ機能部分でも書くか。デバッグは・・・RaspberryPiあたりをホストにしてやればいいか。

・と手をつけ始めたところで、ステートマシンのステート番号をenumできないのかなというところで、Gemini君に聞いてみるとtypedefできるよという。でもなんとなく変だなと思ってもう少しつついてみたらSystemVerilogなら・・・ということ。

・というあたりで、いままでなんとなくスルーしていたSystemVerilogとご対面となる。

・ごちゃごちゃしたところは生成AI君にお尋ねしてみたけど、あまり欲張らないで使うということなら、wireやregをまとめてlogicにすれば良いとか、structが使えるようになっているとか、Verilog+αてきにいけるようだ。

・ところでQuartusは対応しているのかな?と思ったらLiteエディションでもすんなり対応しているらしい。

・で、IcarusVerilogの方もOKらしい。ちょっと試したらエラーが出たのだけど、これは拡張子svで自動判定とはいかなくて、"-g2005-sv”というオプションをつけてやればOK.ちなみにテストベンチは手を加えずにVerilogのままだけど何も文句は言われなかった。C/C++のような関係なのかな?

2025.09.14 19:31

UbuntuでPicoScope

・というところで、久しぶりにPicoScopeを動かしてみる。

・ソフトは?と見に行ったらPicoScope7がリリースされている。Linux,MacOS,Windowsのフル対応だけど、以前試したときは仮想マシン下のLinuxではうまくいかなかったんだっけとか思いながらつらつらとサイトを眺める。

・インストール方法は説明されているとおりで、特別難しいことはない。要するにリポジトリを登録してsudo apt install picoscopeすればいい。

・実機が無くてもデモモードで立ち上げて適当な入力があるかのようにしてプロトコル解析なども試すことができる。なるほど。

・ということで、実機とつないでみる。やってみたら最初に認識されてから再接続されるのだけど、このとき見つからないよということになってしまう。

・やはりだめなのかと思っていた時にふと「こいつはUSB3.xじゃなかったけ?」と思い出して仮想マシンの設定を見たらUSB2.0になっていた。

・これを変えれば良いのかとやってみたらビンゴだったようで、ちゃんと認識されて動き出した。とりあえずアナログチャンネルを試したら結構簡単にいけそう。

2025.09.13 16:49

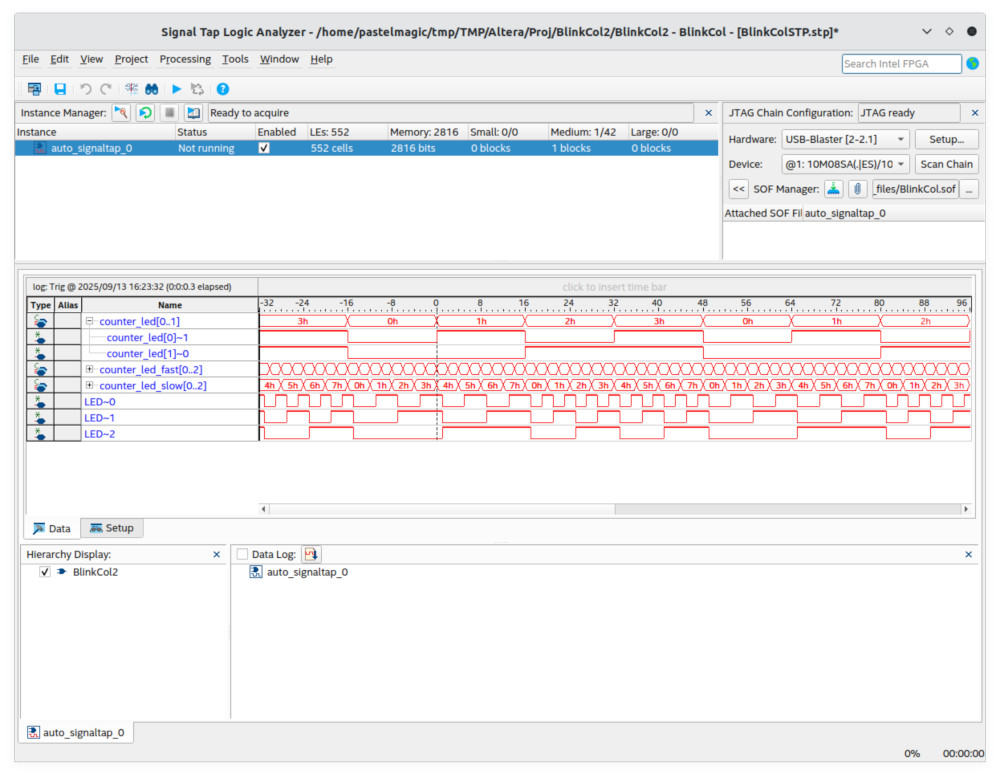

簡単じゃないかSignalTap

・そんなところで、SignalTapを試してみる。XilinxでいうILAと同じようにFPGA内部にろじっくアナライザ相当の回路を組み込んで内部メモリに波形を取り込み、JTAG経由でPCに転送して表示しようというもの。

・Xilinxはあれやこれやと面倒だったのだけどAlteraはどうだろう。

・と、やってみるとなんとシンプルなこと。

1)とりあえずFile=>NewでSignalTapのファイル(*.stp)を作成してSave Asでいったん空ファイル状態でセーブ。

2)右側のSignal Configurationでクロック信号になるものやら取り込みサイズやらを指定

3)左側のところでダブルクリックして観測したい信号やらトリガ条件を追加

4)ビルド

5)右上で.SOFファイルを指定

6)書き込み

7)左上のRun Analysisボタンをクリック

という感じで動かすとこんな感じ。

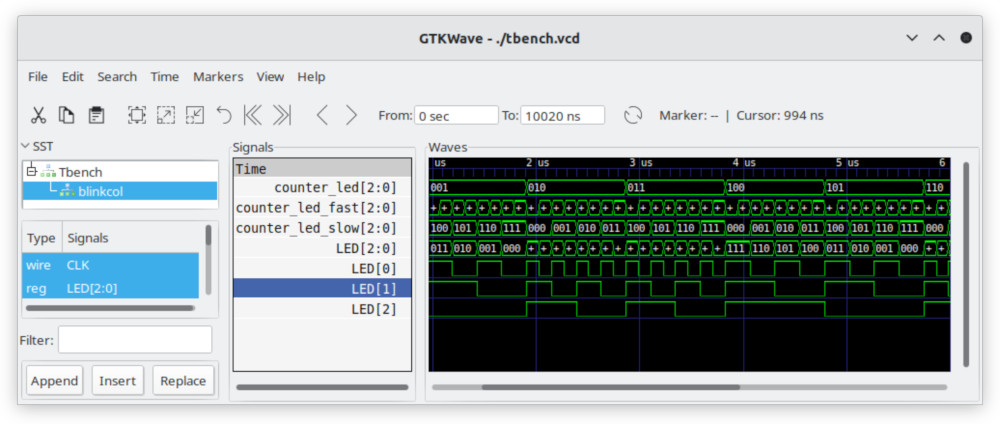

Icarus Verilogでシミュレーションしたときのがこんな感じでまずまず同じ感じ。

・やはりQuartusの方がシンプルだな。最初に触れたFPGAがXilinxのXC3000シリーズだったな。XACTなんてあったっけとか、いろいろ思うけど、やはりこの差を見ているとこれからAltera推しでいこうかな。ブート用の外付けROMも要らないし。という気になる。

2025.09.12 11:24

always @(*)

・verilogでalways @(*)を使えばcaseやらifを使った非同期なセレクタの記述が簡単になるのだけど、果たしてQuartusは対応しているのだろうかとお試ししてみる。

・とりあえずIcarusVerilogのシミュレーションではうまくいっているようなので、QuartusでカラーLEDの点滅パターンを変えて書き込んでみたらうまく動いた。

・さて次はSignalTapでも試してみるか。AMD/Xilinxの方はこのあたりも結構面倒くさかったけど、Intel/Alteraはどうかな。

2025.09.11 15:26

MAX10評価ボード

・MAX10を使うことがほぼほぼ確定。いままで付録基板みたいな小規模なものでいろいろやっていたけど、ぼちぼち少し規模の大きい評価ボードを入手しておく必要がありそうだな。

・なんて思いながら探していたDK-DEV-10M50Cとかいうものが見つかった。DigiKeyで在庫があるらしい。送料含めたらマルツさん経由の方が割安かな。しかし、ご本家Intelさんの写真とマルツさんの写真が違うのは何なのだろう。

・いきなりの豪雨で焦る。都心方面はかなりすごいことになったところもあったようだけど、こちらは普通にすごい雨という程度で、30分もしないうちに僅かなポツポツ雨。

2025.09.10 14:57

ポータブルHDDの収納袋

・少し整理していたらWiMAXのルーターを入れるのに使っていたポーチというのか、ファスナー付きの入れ物が出てきた。

・なんとなく2.5インチのポータブルHDDとサイズが入りそうだなと思って試しに入れてみたらぴったりすぎるくらいのシンデレラフィット。少々キツめだけど外側のポケットにケーブルも押し込めた。

・しかし、まるでHDDっぽくないな。

2025.09.09 06:23

matplotその後

・matplotで一応それっぽいグラフは描けるようになってきた。

・なぜそうなっているのかなと謎なところもあるけど、まぁ良いとしよう。

・まだちょっとわかっていないのが数学の直行座標的にX軸、Y軸・・・x=0とy=0だけを太くしてやる方法。

・グラフの範囲を決めて、その範囲でx=0とy=0のグラフを描いてやれば一応それっぽくできるけど、やり方が美しくない。

2025.09.08 06:17

記憶力は大丈夫そうか

・忘れていたと思ったけど、英単語は頭に残っていた。まだ記憶力はそれなりに大丈夫というのか、昔よりマシそうだなと思っておこう。

・Intelは不調だというけど、ノートPCなどでは相変わらずIntel Coreが多いような感じがするのはなぜだろう。法人向けは安い・・・のかな?